# **4-BIT SHIFT REGISTER**

The SN54/74LS95B is a 4-Bit Shift Register with serial and parallel synchronous operating modes. The serial shift right and parallel load are activated by separate clock inputs which are selected by a mode control input. The data is transferred from the serial or parallel D inputs to the Q outputs synchronous with the HIGH to LOW transition of the appropriate clock input.

The LS95B is fabricated with the Schottky barrier diode process for high speed and is completely compatible with all Motorola TTL families.

- Synchronous, Expandable Shift Right

- Synchronous Shift Left Capability

- Synchronous Parallel Load

- · Separate Shift and Load Clock Inputs

- Input Clamp Diodes Limit High Speed Termination Effects

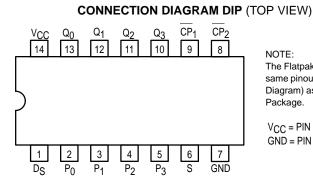

NOTE: The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-Line Package.

LOADING (Note a)

V<sub>CC</sub> = PIN 14 GND = PIN 7

| 4-BIT SHIFT REGISTER<br>LOW POWER SCHOTTKY |                                           |  |  |  |  |  |  |

|--------------------------------------------|-------------------------------------------|--|--|--|--|--|--|

| 14<br>1                                    | <b>J SUFFIX</b><br>CERAMIC<br>CASE 632-08 |  |  |  |  |  |  |

| 14                                         | <b>N SUFFIX</b><br>PLASTIC<br>CASE 646-06 |  |  |  |  |  |  |

| 14 Bettered                                | <b>D SUFFIX</b><br>SOIC<br>CASE 751A-02   |  |  |  |  |  |  |

| ORDERING IN                                | FORMATION                                 |  |  |  |  |  |  |

| SN54LSXXJ<br>SN74LSXXN<br>SN74LSXXD        |                                           |  |  |  |  |  |  |

#### **PIN NAMES**

|                 |                                              | HIGH     | LOW          |

|-----------------|----------------------------------------------|----------|--------------|

| S               | Mode Control Input                           | 0.5 U.L. | 0.25 U.L.    |

| DS              | Serial Data Input                            | 0.5 U.L. | 0.25 U.L.    |

| <u>Po</u> -P3   | Parallel Data Inputs                         | 0.5 U.L. | 0.25 U.L.    |

| <u>CP1</u>      | Serial Clock (Active LOW Going Edge) Input   | 0.5 U.L. | 0.25 U.L.    |

| CP <sub>2</sub> | Parallel Clock (Active LOW Going Edge) Input | 0.5 U.L. | 0.25 U.L.    |

| $Q_0 - Q_3$     | Parallel Outputs (Note b)                    | 10 U.L.  | 5 (2.5) U.L. |

NOTES:

a. 1 TTL Unit Load (U.L.) = 40  $\mu$ A HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74) Temperature Ranges.

### **GUARANTEED OPERATING RANGES**

| Symbol         | Parameter                           |          | Min         | Тур        | Max         | Unit |

|----------------|-------------------------------------|----------|-------------|------------|-------------|------|

| VCC            | Supply Voltage                      | 54<br>74 | 4.5<br>4.75 | 5.0<br>5.0 | 5.5<br>5.25 | V    |

| Т <sub>А</sub> | Operating Ambient Temperature Range | 54<br>74 | -55<br>0    | 25<br>25   | 125<br>70   | °C   |

| ЮН             | Output Current — High               | 54, 74   |             |            | -0.4        | mA   |

| IOL            | Output Current — Low                | 54<br>74 |             |            | 4.0<br>8.0  | mA   |

# SN54/74LS95B

## FAST AND LS TTL DATA

# SN54/74LS95B

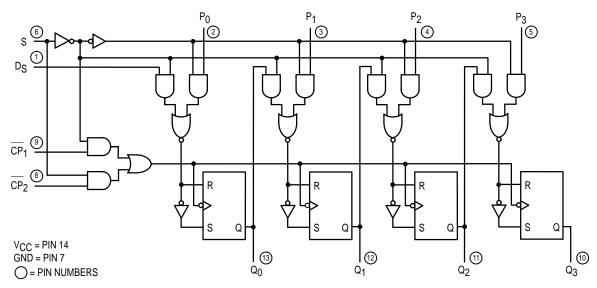

LOGIC DIAGRAM

### FUNCTIONAL DESCRIPTION

The LS95B is a 4-Bit Shift Register with serial and parallel synchronous operating modes. It has a Serial (D<sub>S</sub>) and four Parallel (P<sub>0</sub>-P<sub>3</sub>) Data inputs and four Parallel Data outputs (Q<sub>0</sub>-Q<sub>3</sub>). The serial or parallel mode of operation is <u>con</u>trolled by a Mode Control input (S) and two Clock Inputs (CP<sub>1</sub>) and (CP<sub>2</sub>). The serial (right-shift) or parallel data transfers occur synchronous with the HIGH to LOW transition of the selected clock input.

When the Mode Control input (S) is HIGH, CP<sub>2</sub> is enabled. A HIGH to LOW transition on enabled CP<sub>2</sub> transfers parallel data from the  $P_0-P_3$  inputs to the  $Q_0-Q_3$  outputs.

When the Mode Control input (S) is LOW, CP1 is enabled. A

HIGH to LOW transition on enabled  $\overline{CP}_1$  transfers the data from Serial input (D<sub>S</sub>) to Q<sub>0</sub> and shifts the data in Q<sub>0</sub> to Q<sub>1</sub>, Q<sub>1</sub> to Q<sub>2</sub>, and Q<sub>2</sub> to Q<sub>3</sub> respectively (right-shift). A left-shift is accomplished by externally connecting Q<sub>3</sub> to P<sub>2</sub>, Q<sub>2</sub> to P<sub>1</sub>, and Q<sub>1</sub> to P<sub>0</sub>, and operating the LS95B in the parallel mode (S = HIGH).

For normal operation, S should only change states when both Clock inputs are LOW. However, changing S from LOW to HIGH while CP<sub>2</sub> is HIGH, or changing S from HIGH to LOW while CP<sub>1</sub> is HIGH and CP<sub>2</sub> is LOW will not cause any changes on the register outputs.

| OPERATING MODE |                         | I               | NPUTS           | OUTPUTS             |                     |                |                                                       |                                                                   |                |

|----------------|-------------------------|-----------------|-----------------|---------------------|---------------------|----------------|-------------------------------------------------------|-------------------------------------------------------------------|----------------|

| OPERATING MODE | S                       | CP <sub>1</sub> | CP <sub>2</sub> | DS                  | Pn                  | Q <sub>0</sub> | Q <sub>1</sub>                                        | Q <sub>2</sub>                                                    | Q3             |

| Shift          | L                       | <b>ب</b> ب      | X<br>X          | l<br>h              | X<br>X              | L<br>H         | 90<br>90                                              | 91<br>91                                                          | 92<br>92       |

| Parallel Load  | Н                       | Х               | l               | Х                   | Pn                  | P <sub>0</sub> | P1                                                    | P2                                                                | P <sub>3</sub> |

| Mode Change    | ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ |                 |                 | × × × × × × × × × × | × × × × × × × × × × |                | No Cł<br>No Cł<br>Undete<br>Undete<br>No Cł<br>Undete | nange<br>nange<br>ermined<br>ermined<br>nange<br>ermined<br>nange |                |

L = LOW Voltage Level

H = HIGH Voltage Level

X = Don't Care

I = LOW Voltage Level one set-up time prior to the HIGH to LOW clock transition.

h = HIGH Voltage Level one set-up time prior to the HIGH to LOW clock transition.

P<sub>n</sub> = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the HIGH to LOW clock transition.

# SN54/74LS95B

|                 |                                |        | Limits |       |      |      |                                                 |                                     |  |

|-----------------|--------------------------------|--------|--------|-------|------|------|-------------------------------------------------|-------------------------------------|--|

| Symbol          | Parameter                      |        | Min    | Тур   | Max  | Unit | Test Co                                         | onditions                           |  |

| VIH             | Input HIGH Voltage             |        | 2.0    |       |      | V    | Guaranteed Input HIGH Voltage for<br>All Inputs |                                     |  |

| Ma              |                                | 54     |        |       | 0.7  | V    | Guaranteed Input                                | LOW Voltage for                     |  |

| VIL             | Input LOW Voltage              | 74     |        |       | 0.8  | V    | All Inputs                                      |                                     |  |

| VIK             | Input Clamp Diode Voltage      |        |        | -0.65 | -1.5 | V    | $V_{CC} = MIN, I_{IN} =$                        | –18 mA                              |  |

| Maria           |                                | 54     | 2.5    | 3.5   |      | V    | V <sub>CC</sub> = MIN, I <sub>OH</sub> :        | = MAX, VIN = VIH                    |  |

| VOH             | Output HIGH Voltage            | 74     | 2.7    | 3.5   |      | V    | or V <sub>IL</sub> per Truth T                  | able                                |  |

| Max             |                                | 54, 74 |        | 0.25  | 0.4  | V    | $I_{OL} = 4.0 \text{ mA}$ $V_{CC} = V_{CC}$     |                                     |  |

| VOL             | Output LOW Voltage             | 74     |        | 0.35  | 0.5  | V    | I <sub>OL</sub> = 8.0 mA                        | VIN = VIL or VIH<br>per Truth Table |  |

| l               |                                |        |        |       | 20   | μΑ   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7 V  |                                     |  |

| lΗ              | Input HIGH Current             |        |        |       | 0.1  | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 7.0 V  |                                     |  |

| ۱ <sub>IL</sub> | Input HIGH Current             |        |        |       | -0.4 | mA   | $V_{CC} = MAX, V_{IN} = 0.4 V$                  |                                     |  |

| IOS             | Short Circuit Current (Note 1) |        | -20    |       | -100 | mA   | V <sub>CC</sub> = MAX                           |                                     |  |

| ICC             | Power Supply Current           |        |        |       | 21   | mA   | V <sub>CC</sub> = MAX                           |                                     |  |

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

### AC CHARACTERISTICS (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5.0 V)

|                  |                         | Limits |     |     |      |                                                   |

|------------------|-------------------------|--------|-----|-----|------|---------------------------------------------------|

| Symbol           | Parameter               | Min    | Тур | Max | Unit | Test Conditions                                   |

| fMAX             | Maximum Clock Frequency | 25     | 36  |     | MHz  |                                                   |

| <sup>t</sup> PLH | CP to Output            |        | 18  | 27  | ns   | V <sub>CC</sub> = 5.0 V<br><sup>C</sup> L = 15 pF |

| <sup>t</sup> PHL |                         |        | 21  | 32  | ns   | 2 - 10 pi                                         |

## AC SETUP REQUIREMENTS (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5.0 V)

|                |                         | Limits |     |     |      |                  |

|----------------|-------------------------|--------|-----|-----|------|------------------|

| Symbol         | Parameter               | Min    | Тур | Max | Unit | Test Conditions  |

| tW             | CP Pulse Width          | 20     |     |     | ns   |                  |

| t <sub>S</sub> | Data Setup Time         | 20     |     |     | ns   |                  |

| <sup>t</sup> h | Data Hold Time          | 20     |     |     | ns   | $V_{CC} = 5.0 V$ |

| t <sub>S</sub> | Mode Control Setup Time | 20     |     |     | ns   |                  |

| t <sub>h</sub> | Mode Control Hold Time  | 20     |     |     | ns   |                  |

# SN54/74LS95B

### **DESCRIPTION OF TERMS**

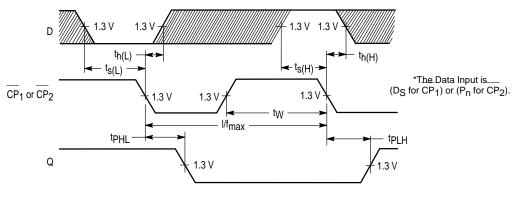

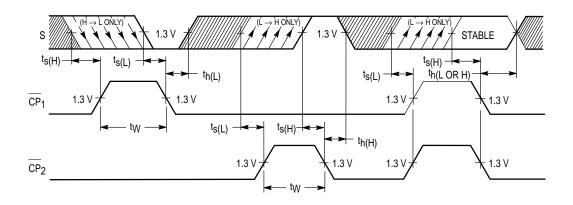

SETUP TIME(ts) —is defined as the minimum time required for the correct logic level to be present at the logic input prior to the clock transition from HIGH to LOW in order to be recognized and transferred to the outputs.

HOLD TIME (th) — is defined as the minimum time following

the clock transition from HIGH to LOW that the logic level must be maintained at the input in order to ensure continued recognition. A negative HOLD TIME indicates that the correct logic level may be released prior to the clock transition from HIGH to LOW and still be recognized.

#### AC WAVEFORMS

The shaded areas indicate when the input is permitted to change for predictable output performance.

Figure 1

Figure 2